-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

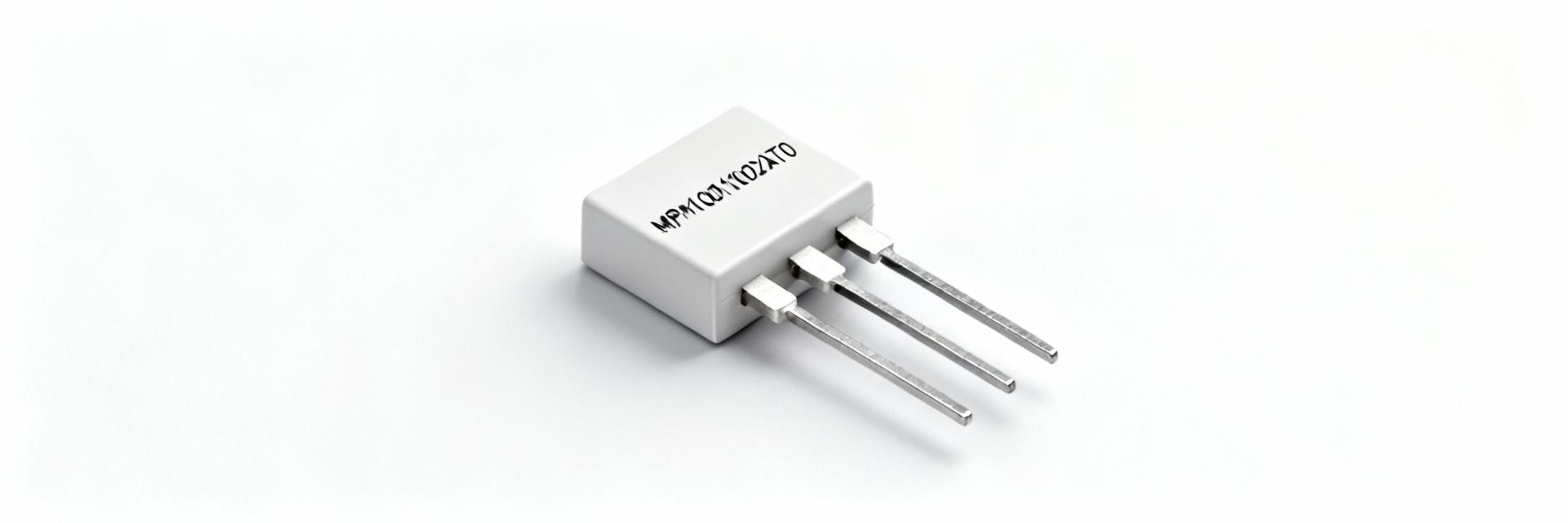

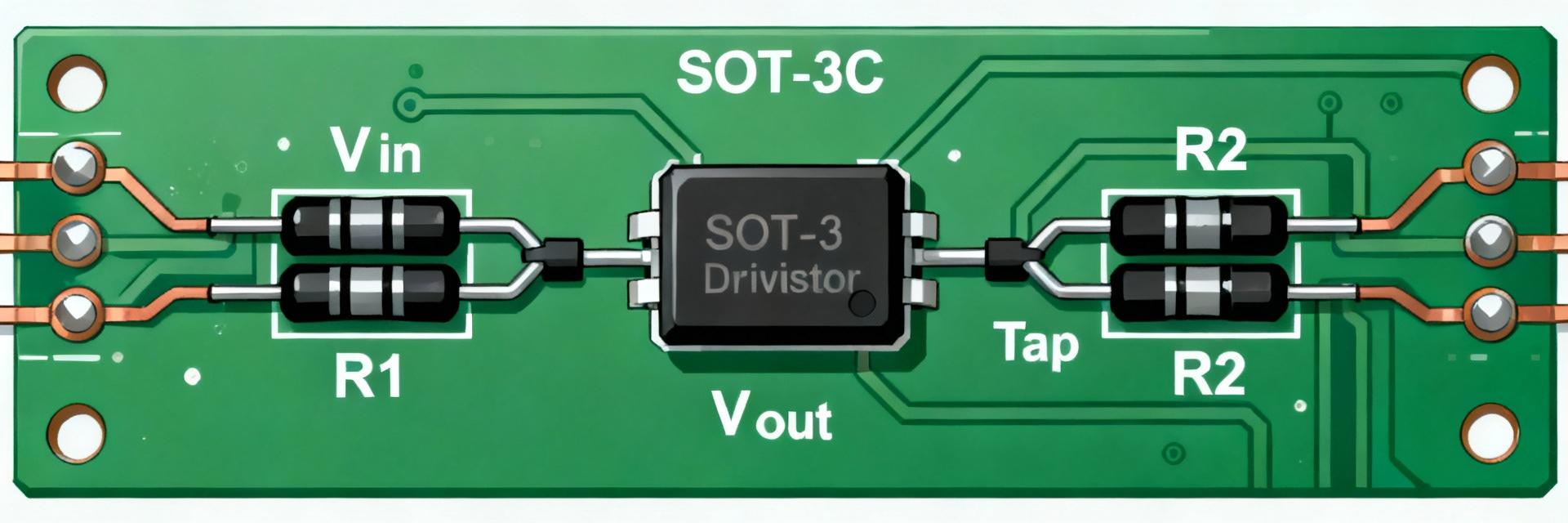

MPMT1002AT5: Complete SOT-23 Divider Specs & Data Sheet

>60% of precision ADC front-end designs use matched thin-film resistor networks in SOT‑23 packages for low-drift scaling and improved CMRR. This note delivers a concise, actionable breakdown of the MPMT1002AT5: what it is, key electrical and mechanical specs, PCB integration tips, application examples, sourcing guidance and where to verify parameters in the official datasheet. The goal is an engineer-ready reference for using this SOT-23 divider in precision front-ends.

The MPMT1002AT5 is presented here as a compact, fixed matched thin‑film resistor network in a SOT‑23 divider footprint. Engineers should consult the official datasheet for authoritative pinout, absolute max ratings and mechanical drawings before design signoff; this article emphasizes practical interpretation and design-impact guidance for quick integration.

1 — What the MPMT1002AT5 Is: Part Overview (Background)

1.1 — Package & Basic Function

The device is a matched thin‑film resistor divider in a SOT‑23 package intended to provide a fixed, accurate resistance ratio for voltage scaling. As a two‑resistor-divider topology it presents a single divided output pin and two end pins; the manufacturer datasheet contains the authoritative pinout and electrical tables. Functionally the part replaces discrete resistor pairs to improve ratio matching, reduce PCB area and lower trimming effort.

1.2 — Typical Applications

Common uses include ADC input scaling, reference/bias networks, op‑amp gain setting and sensor linearization. Example: replacing a discrete 10:1 divider with a matched network reduces systematic ratio error and long‑term drift in precision ADC front‑ends, improving total error budget when amplifier input bias currents and source impedance are managed per the datasheet guidance.

2 — Electrical Specifications (Data Deep‑Dive)

2.1 — Resistance Values, Ratio Tolerance & Tracking

Nominal resistance values and absolute tolerances vary by ordering code; consult the datasheet for the exact nominal set for the chosen device. Ratio tolerance (matching) is the key spec for divider accuracy: for a divider with nominal ratio Rb/(Ra+Rb), small mismatch Δ yields output error approximately Δ_ratio ≈ ΔR / (Ra+Rb) in fractional terms. Designers should use the datasheet ratio tolerance to compute ppm or percentage contribution to the ADC error budget.

2.2 — Temperature Coefficient, Power & Operating Ranges

TCR tracking, operating temperature range and voltage/power limits set the drift and safe‑operating envelope. Typical datasheet entries include TCR (ppm/°C) for absolute and tracking, rated ambient range and maximum continuous voltage. Below is a compact spec summary and design impact; use the datasheet for exact numeric fields for your lot.

| Spec | Typical Value (see datasheet) | Design Impact |

|---|---|---|

| TCR (tracking) | Low ppm/°C | Controls differential drift; critical for long‑term ADC scale stability |

| Operating temp | Industrial range | Derate power and expect additional drift near extremes |

| Max differential voltage / power | Per datasheet | Limits divider placement in high‑voltage front ends; requires derating |

3 — Mechanical, Pinout & PCB Integration (Data + Guide)

3.1 — SOT‑23 Dimensions, Pinout & Footprint

The SOT‑23 divider package offers a compact L×W×H profile with manufacturer mechanical drawing specifying pad land pattern and pin numbering. Follow the datasheet land pattern recommendation for pad size, solder mask clearance and paste mask apertures. A correct footprint prevents tombstoning and ensures solder fillet consistency for this SOT‑23 divider.

3.2 — Thermal and Mounting Considerations

Thermal dissipation is constrained by small package thermal resistance and PCB copper area. Use thermal pours tied to the ground plane, keep trace widths sufficient for power dissipation and avoid placing high‑power components adjacent to the divider. Adhere to the manufacturer reflow profile for peak temperature and dwell times; include the datasheet mechanical drawing in your CAD library filename for traceability.

4 — Application Examples & Design Tips (Method / How‑to)

4.1 — Common Circuit Examples (ADC scaling, Bias networks)

ADC scaling example: for a required scale factor of 0.1, select a divider ratio Rb/(Ra+Rb)=0.1. If Ra and Rb are internal matched elements, total error ≈ ratio_tolerance + TCR-induced drift. Calculate expected Vout = Vin×Rb/(Ra+Rb) and propagate resistor ratio tolerance into ADC LSB error. For op‑amp biasing, use the network to set precise mid‑rail references while minimizing added noise and source impedance.

4.2 — Troubleshooting & Best Practices

Minimize noise by using short traces, guard routing for high‑impedance nodes, and proper bypassing near ADC inputs. Avoid loading the divider with low impedance inputs unless buffered. To validate ratio and TCR on the bench, measure Vout vs Vin across temperature steps and compute fractional deviation against the datasheet ratio tolerance; log results to confirm part lot performance.

5 — Sourcing, Cross‑References & Compliance (Case & Action)

5.1 — Where to Buy, Part Marking & Ordering Options

Purchase through authorized electronics distributors and the manufacturer's sales channels; search the exact part number string and check reel vs. cut‑tape packaging and minimum order quantities. BOM tips: include full ordering code with tolerance and packaging suffix, request reel quantities for production, and document part marking and footprint filename in the BOM comment field to avoid mis‑picks.

5.2 — Equivalent Parts, Cross‑References & Compliance

When seeking equivalents, match ratio tolerance, TCR tracking and package type first, then confirm thermal and voltage limits. Verify RoHS/REACH declarations and any required industrial or automotive qualifications in supplier compliance documents. Always cross‑check electrical tables in the official datasheet before substituting alternate family parts.

Summary

- The MPMT1002AT5 is a compact matched thin‑film SOT‑23 divider that replaces discrete resistor pairs to improve ratio accuracy and drift performance; consult the official datasheet to confirm nominal resistances and pinout for your specific ordering code.

- Key design drivers are ratio tolerance, TCR tracking and maximum voltage/power limits; these determine error budget contribution and placement/thermal strategy on the PCB.

- For reliable integration, add the mechanical drawing and recommended land pattern to the CAD library, follow the reflow profile, and validate divider ratio and drift on the bench before production.

Frequently Asked Questions

What are the nominal resistance values and tolerances for MPMT1002AT5?

Nominal values and absolute tolerances depend on the specific ordering code; consult the official datasheet for the exact resistor values, absolute tolerance and ratio tolerance for the device variant you plan to use. Use those figures to compute the divider's contribution to system gain error and the ADC error budget.

How does the SOT‑23 divider TCR affect ADC scaling stability?

TCR tracking defines how matched resistors change relative to each other with temperature. Even if absolute TCR is modest, close tracking reduces differential drift; compute expected drift contribution by multiplying TCR tracking (ppm/°C) by the anticipated ambient swing and convert to output voltage change relative to Vin.

What PCB footprint and reflow precautions are recommended for MPMT1002AT5?

Use the manufacturer land pattern and solder‑paste aperture recommendations from the datasheet, maintain recommended solder mask clearances, and follow the published reflow profile to avoid tombstoning or excessive stress. Include thermal copper pours if power dissipation approaches datasheet limits and validate solder joints in the first assembly run.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- APT50GH120BSC20 Power Module: Latest Performance Report

- APT50GH120BD30 IGBT: How to Maximize Efficiency for EV Drive

- GTSM20N065: Latest 650V IGBT Test Report & Metrics

- CMSG120N013MDG Performance Report: Efficiency & Losses

- GTSM40N065D Technical Deep Dive: 650V IGBT + SiC SBD

- NOMC110-410UF SO-16: Live Stock & Price Report

- TOMC16031000FT5 Datasheet: Key Specs & Performance

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606